RISC-V

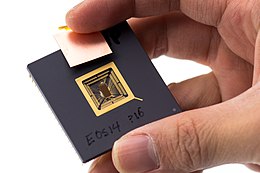

RISC-V Prototypeprosessor som bruker RISC-V-arkitekturen i januar 2013

Prototypeprosessor som bruker RISC-V-arkitekturen i januar 2013

| Type | RISC ISA , prosjekt , instruksjonssett , IT-plattform |

|---|---|

| Nettsted | riscv.org |

RISC-V (uttalt på engelsk "RISC five" som betyr "fem RISC") er en instruksjonssettarkitektur (instruksjonsarkitektur ISA) RISC åpen og gratis , inkludert 32-, 64- og 128-bit c det vil si åpne spesifikasjoner som kan brukes fritt av utdanning, forskning og industri. Den er implementert i forskjellige SoC-er , beregnet for innebygde, tilkoblede objekter (støttet av forskjellige sanntidssystemer eller for innebygde, som Arduino , FreeRTOS , HarmonyOS , LiteOS , RT-Thread , RustOS , Zephyr .. .), lette datamaskiner i form av SBC , vanligvis med Linux ( Debian , Fedora , Ubuntu , Yocto ) eller til og med varianter av OpenWrt , servere , og et europeisk prosjekt startet i 2019, tar sikte på å bruke det i superdatamaskiner innenlands som akseleratorer innen lav -kraft SoC-er utviklet lokalt og kjører under GNU / Linux , som de aller fleste superdatamaskiner.

Motivasjoner

Dette prosjektet, opprinnelig opprettet i informatikkavdelingen ved University of California i Berkeley , USA , var opprinnelig ment for studier og forskning, men ble de facto en standard for åpen arkitektur i bransjen.

Målet med dette prosjektet er å lage en åpen standard for driftssystemermikroinstruksjonssett, .

Historisk

Prosessoren utforming starter i 2010 ved University of California, Berkeley, for å utvikle en prosessor med kunnskap om XXI th århundre , ikke å måtte dra kompatibilitet med gamle arkitekturer 20 år som ARM eller Intels x86 -arkitektur og samtidig som ønsker at ISA- arkitekturen ( processor instruction set ) skal være åpen.

I 2014 ble versjon 2.0 av spesifikasjonene publisert, flere store produsenter var interessert i prosjektet.

I 2015 ble RISC-V-stiftelsen opprettet med mer enn 100 medlemmer, og et styre bestående av selskaper som Google , Nvidia , Western Digital , NXP Semiconductors , Microsemi og Bluespec , samt representanter fra University of Berkeley. Siden den gang har selskaper som AMD , Qualcomm og IBM sluttet seg.

I 2016 planlegger Nvidia å bruke en RISC-V-mikrokontroller for GPU-ene og forventer dermed å tredoble ytelsen sammenlignet med sin egen mikrokontroller, Falcon. Falcon er også en RISC-arkitekturprosessor, men med begrenset 32-biters adressering og ingen trådbeskyttelse og med begrensninger. Nvidia ønsker derfor å erstatte den med 64-bitersversjonen av RISC-V, og dermed dra nytte av 64-biters adressering, feilretting, et utvidbart instruksjonssett og forbedret sikkerhet.

I 2017 ble versjon 2.2 av spesifikasjonene gitt ut. Mozilla kunngjør at Rust- språket kan samles til RISC-V-arkitekturen. Produsenten av harddisker, Western Digital kunngjør, at den vil levere milliarder av utstyret sitt, med en kontrollerarkitektur RISC-V.

de 9. juli 2018, en del av ledelsen i selskapet ARM bestemmer seg for å opprette et nettsted med navnet “riscv-basics.com” mot RISC-V, og føler at markedet er truet, spesielt fordi en betydelig del av de største kundene (nevnt ovenfor) også er begynner å utvikle løsninger basert på RISC-V. Denne handlingen opprørte det tekniske personalet i selskapet som så på det som et angrep på åpen kildekode-bevegelse. Det har også den effekten å øke bevisstheten om RISC-V litt mer og skape større bevissthet om at det er et levedyktig alternativ. Ledelsen i ARM bestemmer seg til slutt for å stenge nettstedet neste dag, den10. juli 2018.

I 2019 legger den amerikanske regjeringen til Donald Trump press på grunnleggerne av mikroelektronikk, som den taiwanske TSMC , den viktigste i verden, for å flytte til amerikansk jord, som sistnevnte nekter, alt ved å true de som vil fortsette å samarbeide med kinesiske selskaper som Huawei . Etter den politiske risikoen ved dette presset, bestemte stiftelsen seg for å etablere seg i et nøytralt land: Sveits .

I oktober 2019, Nvidia leter etter RISC-V-spesialister for å integrere den som prosessor i sine Tegra SoC-er .

I oktober 2020, Huawei lanserer sine første maskinvare- og programvareutviklingssett for sine nye interne mikrokontrollere, de bruker en kompilator mot RISC-V-arkitekturen.

I Juli 2021, Haiku blir portet til RISC-V, Debian Bulleseye- funksjonen fryser for utgivelsen av den første versjonen av distribusjonen for å offisielt støtte RISC-V. Radeon HD grafikkdriver for Linux kjører på arkitektur.

Spesifikasjoner

Den implementerer et RISC-instruksjonssett, uten mikrokode , eller overlegg av arkitektur av typen utførelse i forstyrrelsen eller i rekkefølgen, eller støtten til en type materiale spesielt ( ASIC , FPGA ...), men de -ci kan implementeres med alle funksjonene deres.

- 2008 revisjon av IEEE-754-standarden for enheten for beregning av flytende nummer .

- 32, 64 eller 128 bit adressering.

- Mulighet for hver implementering å gi utvidede instruksjoner.

- Støtte for svært parallell implementering av flere kjerner og heterogen flerprosessorarkitektur.

- Valgfrie instruksjoner med variabel lengde, som både øker tilgjengelig ledig kodingsplass, men også gjør instruksjonene tettere for å forbedre ytelsen, redusere statisk kodestørrelse og effektivitet.

- En helt virtualizable arkitektur for å lette hypervisor utvikling .

Forskere ved University of California , Berkeley , har også utviklet en versjon som heter BOOM, og legger til ordreutførelse av instruksjoner i RV64G-modellen.

Utvidelsesnomenklatur

Navnet på prosessoren har en betydning:

- Basen består av RV (for RISC-V), deretter 32, 64 eller 128, avhengig av antall biter, og til slutt en I eller en E (innebygd, det vil si innebygd).

De mulige basenavnene er derfor:

- RV32I

- RV32E (ombord)

- RV64I

- RV128I

Navnet på prosessoren blir fulgt av en eller flere bokstaver som beskriver utvidelsene som legges til databasen:

- M - Standard utvidelse m ultiplikasjoner og hele divisjoner;

- A - Standard instruksjonsutvidelse har tomiques ;

- F - Standard enkelt presisjon flytende punkt f utvidelse (32 bits);

- D - standard flytende punktet Forlengelse d ouble presisjon (64 bits);

- G - G eneral, stenografi for grunnleggende instruksjoner, og instruksjonssettene ovenfor, det vil si M, A, F, D)

- Q - Standard q uadruple presisjon (128 bit) floating point forlengelse ;

- L - standard flytende punktet forlengelse, desimert den ;

- C - Standard instruksjonsutvidelse c ompressées;

- B - Standardmanipulering Extension b ict;

- J - Standard utvidelse av dynamisk oversatte språk ( Compilation on the fly , J ust in time eller JIT), dette gjelder skriptspråk som C # , Haskell , Java , JavaScript , Lua , OCaml , PHP , Python , R , Ruby , Scala , WebAssembly , etc;

- T - Standard minneutvidelse t ransactionnelle;

- P - Standard instruksjonsutvidelse SIMD com p nedskrevet ( P acked SIMD );

- V - Standard utvidelse av operasjoner v ectorielles ;

- N - Standard biapparat i n bruker terruptions;

- S - Standard utvidelse av S upervisor ;

- H - Standard H ypervisor-utvidelse , ligner på S men starter med en S.

Grunnleggende 32-biters ISA

Den grunnleggende instruksjonssett består av 47 instruksjoner, inkludert åtte systeminstruksjoner (systemanrop , krav tellere), resten blir fordelt på det kategorier beregningen, strømningsstyring og hukommelsesaksess.

RV32I-versjonen har 32 32-biters generelle registre, mens RV32E-versjonen (innebygd, innebygd ) bare har 16 32-biters generelle registre. Begge har også et PC-register.

BeregningsinstruksjonerAlle beregningsinstruksjonene bruker tre operander, bortsett fra luiog auipcsom bare har to (et destinasjonsregister og en umiddelbar verdi). Den første operanden er destinasjonsregisteret, det andre kilderegisteret og det tredje, enten et andre register eller en øyeblikkelig verdi (spesifisert av a ii mnemonikken til instruksjonen, bortsett fra å auipcha en annen betydning) (Multiplikasjonsinstruksjoner og divisjonstall er inneholdt i forlengelse M):

- add, addi, sub : Addisjon og subtraksjon addi brukes sammen med en negativ umiddelbar verdi for subtraksjon av en øyeblikkelig verdi.

- sll, slli, srl, srli, sra, srai : Bit skift bit ( s hift ) + venstre / høyre ( en), logikk ( l ogical ) eller aritmetisk ( en rithmetic ).

- and, andi, or, ori, xor, xori : Logiske operasjoner bitvis inkludert og ( og ), eller ( gull ) og eksklusive OR ( XOR ).

- slt, slti, sltu, sltui, ( S , og hvis det ess t Han- ) setter destinasjonsregister til 1 hvis den første kilden operanden er lik eller mindre enn den andre. Den usignerte u- signeringen ( u underskrevet ). Umiddelbare operander er begrenset til 12 bits.

- lui, laster den viktigste øyeblikkelige delen ( l oad u pper i mmediate ), dvs. bitene 12 til 31 i destinasjonsregisteret med en umiddelbar 20-biters verdi. Den må brukes addimed en umiddelbar 12-biters verdi for å fullføre verdien.

- auipclegger til den umiddelbare verdien til de 20 mest betydningsfulle bitene til den ordinære telleren (PC), den må også brukes additil de 12 minst signifikante bitene

Betinget forgreningsinstruksjon:

- beq, bne, blt, bltu, bge, bgeu, Instruction gren ( b ranch ) betinget av at to operatører, dvs. ( e kv ), annen ( n ot e kv ), er mindre ( det ittler t Han ), er større enn eller lik ( g reater gull e kv ) signerte (standard) eller ikke ( u nsigned ).

Ubetingede forbindelser:

- jal( J ump en nd l blekk ), går kontrollen til adressen til PC til hvilket det tilsettes den umiddelbare 20-bits signert verdien. Legger til adressen til neste instruksjon (returadresse på slutten av den ringte funksjonen) i destinasjonsregisteret.

- jalr( j ump a nd l ink, r egister ), blir hoppadressen beregnet ved å legge til kilderegisteret og den umiddelbare 12-bitersverdien, og instruksjonsadressen lastes inn i destinasjonen. Hvis denne instruksjonen er foran en auipc-kommando, kan hoppet utføres i hele 32-biters minne.

Instruksjoner for minnetilgang brukes til å overføre data mellom et register og minne. Den første operanden er registeret, den andre et register som inneholder adressen, den tredje en umiddelbar 12-bits signert verdi lagt til innholdet i registeret som brukes til adressering, for å bestemme den endelige adressen:

- lb, lbu, lh, lhu, lw, Loading ( l oad ) en bitgruppe ( b YTE ), halfword ( h alf-ord , 16-bit) eller ordet ( w ord , 32 bits) fra hukommelsen til en destinasjonsregister. Instruksjonene utvides med tegnet (standard) eller med nuller ( u underskrevet ).

- sb, sh, sw, Lagring ( s torus ), en byte ( b YTE ), halfword ( h alf-ord , 16-bit) eller ordet ( w ord , 32 bits) til minnet.

- fence, tvinger planleggingen av minnetilgang i en flertrådet sammenheng, spesielt ved å sikre konsistensen til cachene.

- fence.i, gjør det mulig å sikre at operasjonene fra lagring til instruksjonsminnene (for eksempel instruksjonsbuffer) er fullført før de utføres. Det brukes hovedsakelig i tilfelle av selvmodifisert kode.

En uttalelse brukes til å påkalle et systemanrop, og en annen setter opp et bruddpunkt for feilsøkingsprogrammet :

- ecall, systemanrop

- break, og legger til et bruddpunkt.

Seks instruksjoner brukes til å lese og skrive i systemets kontroll- og statusregistre ( kontroll- og statusregister CSR). CSR-registeret leses i et generelt register, og oppdateres deretter atomisk:

- csrrw, csrrwi, csrrc, csrrci, csrrs, csrrsi,

Følgende 6 32-biters CSR-registre (som tilsvarer 3 64-biters verdier for kjøringsteller) er definert som skrivebeskyttet:

- cycle, cycleh, Syklusteller klokker medgått etter et referansetidspunkt. Denne tiden kan variere hvis DVFS-modus ( Dynamic Voltage and Frequency Scaling) er aktiv.

- time, timeh, I sanntid teller medgått etter et referansetidspunkt (typisk systemoppstart);

- instret, instrethCounter av prosessorinstruksjoner utføres ( inst ruction ret IRED ).

Grunnleggende 64-biters ISA

64-biters ISA utvider registerene og adresseringsområdet fra 32-bit til 64-bit (XLEN = 64). Instruksjoner med suffikset W ( engelsk : W ord , som betyr ord ), indikerer at deres handling er begrenset til ett ord (32 bits) og ikke berører de øvre 32 bitene av inngangene. Signaturen bit blir beveget til den 64 te bit (bit 63) av registrene, slik at det er viktig å benytte spesialiserte funksjoner med 32-bit data.

Dette har også implikasjoner for umiddelbar drift. For eksempel tilsetter addi umiddelbar tilleggsoperasjon med en umiddelbar 12-biters verdi, addiw ignorerer 32-bit overløp, og plasserer tegnbiten på bit 63 i registrene.

Grunnleggende 128-bit ISA

Vector utvidelse

Vektorforlengelsen har tre variabler, ELEN (antall biter av et element), VLEN (antall biter av en vektor) og SLEN (avstand (stripping) mellom to elementer) som alle må være en styrke på 2.

Den inkluderer 32 vektorregister kalt v0 til v31, det er mulig å gruppere to, i det som kalles gruppe av vektorregister ( vektorregistergruppe ) for å forbedre nøyaktigheten eller forbedre ytelsen. Det er også seks Control and Status ( CSR) -registre (vstart, vxsat, vxrm, vtype, vl, vlenb).

GPU

RV64X GPUEn arbeidsgruppe foreslår i Januar 2021en GPU-utvidelse kalt RV64X, spesielt basert på vektorprosessorutvidelsen og VBlock-formatet som er foreslått av Libre GPU- prosjektet, og som kan implementeres i ASIC eller FPGA. Den første versjonen tar sikte på å bruke en driver som er kompatibel med Khronos Vulkan API , for senere å støtte OpenGL og Direct3D . Den bør også i utgangspunktet adressere feltet ombord. Begrensningene som er satt er:

- 64-bit instruksjon;

- Støtte for komplekse funksjoner sin , cos , atan , pow , exp , log , rcp, rsq, sqrt , etc.

- Av vektorer som bærer 2-4 elementer 8, 16 eller 32 bits;

- Av matriser kvadrat 2 × 2, 3 × 3 og 4 × 4;

- piksler i 8, 16, 32 og 64 bit formater;

- Punktene i 4 dimensjoner XYZW, 64 eller 128 bits;

- De piksler 4 RVGA komponenter, med 8, 16, 24 eller 32 biter per komponent;

- De teksler har UVW 3 komponenter, 8 eller 16 bits;

- Støtte for lysvariabler, Ia, ka, Id, kd, Is, ks ...

I desember 2019, Think Sillicon-selskapet foreslo en GPU basert på RISC-V-arkitekturen.

En annen RISC-V-basert GPU, avbruttI 2018 hadde Kazan eller Libre RISC-V-prosjektet som mål å utvikle en GPU basert på RISC-V. I 2020, på grunn av ulike uenigheter med funksjonen til RISC-V-stiftelsen, orienterte forfatterne av prosjektet seg til en OpenPower-arkitektur, åpen versjon av Power , RISC-arkitekturen fra 1990-tallet fra IBM . Forfatterne slår endelig på etableringen av en vektorprosessorutvidelse kalt SV for Power-arkitekturen, nær V-utvidelsen av RISC-V, snarere enn utviklingen av en GPU.

Programvarestøtte

Det foreslås en serie gratis verktøy for utvikling av denne arkitekturen, inkludert kompatibiliteten til GCC- og LLVM-kompilatorene (derfor Clang ), støtten til GDB- feilsøkingsprogrammet , samt QEMU- hypervisor og emulator . Rust- språket har støttet RISC-V siden november 2017.

På assembler nivå , GNU Assembler støtter 32 og 64 bit RISC-V arkitekturer (assembler, Disassembler), og riscv-assembler er en assembler i Python .

Bronzebeard er en RV32IMAC montør skrevet i Python bindemiddel montert program i et minimalistisk bibliotek for å gi et system av det blanke metallet (In) . Den ble først testet på kort fra Sipeed, Longan Nano og Wio Lite, og deres GigaDevice GD32V-prosessor på grunn av muligheten for lett tilgang til denne typen materiale med skjermen for mindre enn 10 €. Forfatteren planlegger å portere den til HiFive1 Rev B. Den samme forfatteren har også produsert en Forth bare metal- tolk for RISC-V.

Denne arkitekturen støttes i januar 2016av Linux-kjernen via et sett med oppdateringer samt av FreeBSD. Integrasjonen i den stabile Linux-kjernen har vært effektiv siden versjon 4.15, med mer omfattende støtte siden versjon 4.17.

Den MicroPython skriptspråk , en versjon som er innrettet til å Python mikrokontrollere , ble overført i 2017 av Micro til RISC-V-arkitektur.

Arduino kjører på GD32V mikrokontrollere fra GigaDevice . Den kan bruke RT-Thread sanntidssystem og RTT-GUI grafiske grensesnitt fra Arduino for dette.

Zephyr- sanntidssystemet fungerer også på RISC-V-prosessorer, spesielt med emulering av Qemu og på forskjellige maskinvareimplementeringer.

Minimumsversjonen av Rust for innebygd (Minimum Supported Rust Version (MSRV)) blir portet til RISC-V, av det rustinnebygde samfunnet. RustOS- systemet , basert på en rCore-kjerne, en Rust- versjon av uCore OS Plus kjører på Qemu-implementeringen av RISC-V og på HiFive Unleashed-systemer, og brukes ved Tsinghua University for operativsystemtimer.

Firmaet UltraSOC utvikler "Tessent Embedded Analytics", en analyse- og sporingsløsning på RISC-V, for proprietære eller åpne løsninger. Den ble kjøpt av Siemens- gruppen og fortsetter denne aktiviteten i gruppen.

Denne arkitekturen støttes av operativsystemene for Internet of Things , LiteOS (BSD-lisens) og mobile plattformer HarmonyOS fra Huawei .

Programvaren for å bidra til å oppdage sikkerhetsproblemer, for å være i stand til å utnytte dem, av den USA etterretningstjenesten , NSA , Ghidra støtter binært format av denne arkitekturen.

I januar 2020Alibaba demonstrerer Android 10 portert av T-hode på sin ICE EVB SoC med 2 XuanTie C910 64-bit RISC-V kjerner, en XuanTie C910V vektor kjerne og en GC8000UL live GPU .

Operativsystemer for servere og stasjonære datamaskiner

Ulike Linux-distribusjoner er tilgjengelige, inkludert Debian Bullseye med mer enn 95% av portede pakker, Fedora , Ubuntu , Yocto . FreeBSD- og Haiku- operativsystemene starter også på RISC-V.

Linux og Haiku kan dra nytte av akselerasjonen av AMD Radeon HD-grafikkort via den gratis Mesa-driveren, som er uavhengig av prosessorarkitekturen.

Programvareemulatorer

Det er mulig å simulere disse arkitekturene via forskjellige emulatorer og hypervisorer.

QEMU hypervisor , samt av ANGEL (en RISC-V-simulator i HTML5 og JavaScript ) eller via ZedBoard- og Zybo- kort med Xilinx Zynq FPGA-er . RISC-V-emulering (32 og 64 bits) støttes naturlig i Qemu fra versjon 2.12.0 utgitt på24. april 2018. Versjon 5.1 legger til støtte for valg av bio i argumenter.

TinyEMU av Fabrice Bellard (også forfatter av QEMU og ffmpeg ) er en lett RISC-V-emulator, den brukes til havnen i Haiku (gratis nyinnspilling av BeOS ). Den brukes også i BareDoom, en port av Doom på RISC-V via Barebox , denne versjonen av TinyEMU selv blir kompilert på nytt i WebAssembly (WASM) for å kjøre i en nettleser.

Juice-VM er en minimalistisk RISC-V RV64IMASU virtuell maskinemulator , som støtter MMU og UART I / O. Det gjør det mulig å kjøre FreeRTOS, og også på systemer med svært begrensede ressurser, for eksempel dual-core ESP32 Xtensa- mikrokontrollere med 8 MB PSRAM og 2 MB SPI-blits, er Linux 5.0-kjernen samlet for RISC-V-arkitektur.

RISC-V Rust er en RISC-V emulator utviklet i Rust språk og kjører i WebAssembly. Målet er å bruke emulatoren i en nettleser. Operativsystemene GNU / Linux og xv6 -riscv fungerer på det.

Maskinvareimplementeringer

utviklingsverktøy

Wrap-V er en RISC-V-kjernegenerator, som også støtter MIPS-arkitektur i TL-Verilog (Transaction Level Verilog ) og går gjennom M4- makroprosessoren . Det gjør det mulig å utvikle kjerner hvis rørledninger har 1 til 7 nivåer. Det er mulig å modifisere M4-utgangen for å tilpasse den til spesifikke behov. Det er også mulig å bruke TL-meisel .

Gratis implementeringer

Den gratis LowRISC- mikroprosessoren er et gratis og åpent implementeringsprosjekt for RISC-V, opprettet av Andrew Huang (fra MIT , også forfatter av den åpne plattformen Novena ), Julius Baxter ( OpenRISC- prosjekt og Cambridge University ), Michael B. Taylor ( University i California i San Diego , UCSD Center for Dark Silicon), Dominic Rizzo ( Google ATAP (en) ), Krste Asanović ( University of California i Berkeley ).

NEORV32 er en gratis implementering ( BSD-lisensparagraf 3) av en plattformuavhengig mikrokontroller-type SoC for FPGA-er skrevet i VHDL. Den er kompatibel med RISC-V 2.2-spesifikasjonen for RV32 og består samsvarstesten. FreeRTOS har blitt portet til denne SoC. Den er basert på arbeidet som utviklere måtte neo430, en implementering av en mikrotype FPGA-prosessor som er kompatibel med MSP430 fra Texas Instruments .

PicoRV32 er en gratis implementering, under ISC-lisens , og støtter RV32IMC instruksjonssett hvis mål er å ha minst mulig fotavtrykk, med valget mellom 750 og 2000 LUT og en maksimal frekvens på 250 til 450 MHz. Hensikten er å være en hjelpeprosessor på en FPGA eller ASIC. Den kan konfigureres som en RV32E-, RV32I-, RV32IC-, RV32IM- eller RV32IMC-kjerne (se delen #Nomenclature of extensions ).

Western Digital tilbyr en rekke kjerner kalt SweRV, åpen kildekode, tilgjengelig via CHIP Alliance. De kunngjorde også et samarbeid med Codasip for å tilby kommersiell støtte til disse hjertene. Disse høytytende prosessorene er rettet mot innebygde domener og støtter instruksjonssettet RV32IMC. SweRV-familien er fordelt på følgende måte:

- SweRV EH1 Superscalar Core har to kjørekøer og er basert på en 9-trinns rørledning.

- SweRV EH2 flertrådet superscalar-kjerne kan håndtere 2 tråder samtidig med 9 rørledningsetapper.

- SweRV EL2 kjerne enkeltuttak med 4 rørledningstrinn.

Det kinesiske vitenskapsakademiet ga ut Xiangshan- prosessoren , under en gratis lisens ( Mulan v2-lisens , OSI- godkjent ) den11. juni 2021på Github . Prosessoren er utviklet på meiselspråk , som ifølge utviklerne har 5 ganger færre kodelinjer enn i Verilog og gir raskere utvikling. På tidspunktet for utgivelsen støtter prosessoren Debian Bulleseye-distribusjon for RISC-V. En første maskinvareimplementering kommer ut iJuli 2021, kalt Yanqihu, gravert i 28 nm og frekvens mellom 1,2 og 1,3 GHz, den har ytelse per GHz som ligner på ARM Cortex-A72 med 7 / Ghz SPEC CPU 2006. En andre versjon planlagt høsten samme år kalt Nanhu, gravert i 14nm og opererer ved 2 GHz, skal nå ytelse per GHz som ligner på en Intel i9-10900K (11.08 / Ghz) med 10 / Ghz SPEC CPU 2006, og en datakraft, på denne frekvensen, sammenlignbar med den til en ARM Cortex- A76 .

Proprietære RISC-V-implementeringer

SiFive, kunngjør en oppstart i juli 2016Den SiFive U5 Coreplex , ved hjelp av RISC-arkitektur og V for implantering U54 opptil åtte kjerner per SoC , hver omfattende instruksjon buffer og data 1 st nivå, SoC omfatter en større buffer 2 e nivå. Målet vil være å først implementere versjoner for veldig spesifikk maskinvare som ikke trenger mye strøm, men spesialiserte funksjoner først, for å kunne forbedre teknologiene senere.

I 2018, oppstarts SiFive, laget av utviklerne av RISC-V, presentert ved FOSDEM den HiFive utløste kort , omfattende en SiFive Freedom U540 SoC prosessor (4 + 1 RISC-V kjerner opp til 1,5 GHz) og 8 Gio av ECC RAM, GB Ethernet-port, og i stand til å kjøre GNU / Linux .

Shakti er et indisk initiativ for design av forskjellige prosessorer basert på RISC-V-arkitekturen og delt inn i 6 serier: E-klasse for innebygd, C-klasse for mikrokontrollere, I-klasse for mikroprosessorer for tynne klienter, M-klasse for kontorautomatisering , S-klasse for arbeidsstasjoner og servere, og til slutt H-klasse for superdatamaskiner.

Codasip er det første selskapet som har utviklet en ikke-fri RISC-V-kompatibel kjerne i januar 2016(Codix) og fortsatte tilbudet med kjernefamilier for innebygde områder og applikasjonsområder. Kjernene utviklet av Codasip er skrevet på CodAL, et språk for arkitekturbeskrivelse. Studio-verktøyet brukes til å skaffe simulatorene og filene som er nødvendige for den fysiske implementeringen av disse kjernene.

L-familien samler 32-bits kjerner med lav effekt, rettet mot innebygde domener, og tilbyr en valgfri beregningsenhet for flytende punkt. Denne familien er tilgjengelig i tre eller fem ledningsfaser.

H-familien samler 64-biters kjerner med høy ytelse rettet mot innebygde domener, og tilbyr en flytende beregningsenhet som et alternativ.

A-familien er 64-biters kjerner som kan kjøre Linux, med muligheten til å utvide dem med "P" -utvidelsen. Disse kjernene har 7 rørledningstrinn, en flytende beregningsenhet, en MMU. I tillegg integrerer -MP-versjonene nivå 1 (L1) og 2 (L2) cacher og støtter opptil 4 kjerner per klynge.

URISC-V-kjernen som er tilgjengelig i Codasip Studio er ment for læring eller testing.

Innebygde og mikrokontrollere

På 7 th RISC-V Workshop , kunngjorde Western Digital at selskapet ville utvikle RISC-V-prosessorer. Western Digital har som mål å starte en overgang til åpen kildekode-løsninger for lagringsserverne. Til slutt forventer WD å selge nesten to milliarder RISC-V-prosessorer per år.

I 2018 presenterte den Grenoble-baserte oppstarten fabless GreenWave GAP8, en prosessor med lavt forbruk for IoT, optimalisert for kunstig intelligens .

I 2019 lanserer GigaDevice Semiconductor GD32V- serien av mikrokontrollere, basert på 32-biters versjon av arkitekturen. Blant de 14 versjonene er GD32VF103 klokket på 108 MHz og får tilgang til det integrerte flashminnet uten ventetid (in) , derfor uten ventetid. Den har 128 KiB flash-minne på chip og 32 KiB SRAM , 2 12-bit analog-til-digital og 2 12-bit digital-til-analog-omformere, samt forskjellige kommunikasjonsgrensesnitt (3 SPI, 2 I2C , 3 USART, 2 UART, 2 I2S, 2 CAN og 1 USB OTG). Brikken er pin-to-pin-kompatibel med GD32-mikrokontrollere basert på ARM-arkitekturen , så vel som STM32 fra STMicroelectronics , noe som gjør det enkelt å portere applikasjoner fra en arkitektur til en annen og også Arduino- kompatibel . GD32V brukes spesielt i utviklingsstyret for Sipeed Longan Nano .

Sipeed har også utviklet Sipeed M1 (eller Kendryte KD233) -kortet, utstyrt med en Kendryte K210 SoC bestående av 2 64-biters RISC-V-kjerner og en kunstig intelligensprosessor. Disse kortene er designet for å fungere med FreeRTOS . Dette kortet bruker MAIXPy, en passende versjon av MicroPython, programmerbar via Plateform.IO. Det finnes forskjellige varianter, for eksempel MaixDuino , hvis kort har et format som er kompatibelt med Arduino , og støtter IDE. Det er også mulig å bruke det med et Linux- operativsystem . Andre, mer kompakte versjoner er tilgjengelige. IJuli 2021 Canaan ga ut Kendryte K510, en forbedret versjon som består av en mikroprosessordel bestående av to RV64-kjerner og en gasspedal bestående av en annen RV64 med DSP-utvidelse.

I 2019 truer USAs president, Donald Trump, med å blokkere leverandørene av Huawei, inkludert grunnleggere som TMSC, og det britiske selskapet ARM, som til da ga IP for kjernene som ble brukt i HiSilicon- prosessorer. Fra Huawei. Det amerikanske selskapet Nvidia hadde kjøpt rettighetene til selskapet ARM fra den japanske SoftBank , Huawei måtte finne en løsning og ser ut til å ha henvendt seg til RISC-V. De første HiHope HiSpark Wifi IoT-utviklingssettene bruker en Hisilicon Hi3518 mikrokontroller, kompatibel med de nye plattformene, Huawei LiteOS og HarmonyOS . Kompilatorene som følger med er GCC- kompilatorer beregnet på 32-biters RISC-V-arkitekturkoder.

I Juli 2021, Kunngjør Espressif tilgjengeligheten av en ny NodeMCU- modell basert på ESP32-C3- prosessor , RISC-V-arkitektur.

NettverksmodulerOpenWifi , presentert idesember 2019, er en åpen kildekode, Linux-kompatibel WiFi-stabel som kan kjøres på FPGA, en funksjonell implementering er gjort på Xilinx FPGA, koblet til fmcomms2 / fmcomms4 RF-kort

Bouffalo Labs BL602 / BL604-moduler, basert på 32-biters RISC-V, er WiFi og Bluetooth 5.0 LE-moduler. Sipeed og Pine64 bør integrere dem i kartene sine for IoT.

I november 2020, Espressif kunngjør lanseringen av ESP32-C3, WiFi & BLE , en prosessor i tråd med ESP32 , men pin-to-pin kompatibel med ESP8266 , og bruker 32-biters RISC-V-arkitektur i stedet for Xtensa LX6. Den har en kryptografisk prosessor, men ingen DSP i motsetning til ESP32.

RomDet europeiske romfartsbyrået utvikler en nevral prosessor kalt " NOEL-V " og basert på ISA RISC-V og dens vektorforlengelse (V eller RVVE) ved bruk av RHBD (Radiation Hardened By Design) -teknologi, for begrensningene i rommiljøet ( temperatur og ioniserende stråler), så vel som energieffektivitetsbegrensninger, i hjertet av satellitter. Prosjektet ledes av Cobham Gaisler, ved European Center for Space Research and Technology (ESTEC), som allerede hadde produsert i 2019, en lignende prosessor kalt " LEON " basert på SPARC -V8- arkitekturen på slutten av 1990-tallet.

DiversePinecil fra Pine64 er et elektronisk regulert loddejern basert på en 108 MHz RISC-V RV32IMAC " Bumblebee Core " prosessor .

Sipeed RV-Debugger Plus er en åpen kildekode UART-kontakt (seriell) og JTAG- feilsøking , basert på Bouffalo Lab BL702 SoC, ved hjelp av en 32-biters, 144 Mhz RISC-V-mikrontroller, bestående av en FPU, en krypteringsmodul, Audio (I2S master / slave), styrer den Zigbee 6, Bluetooth 5.0 LE, WiFi og internett. Firmware er gratis programvare , det er også mulig å bruke den som et utviklingskort.

FPGA

ZedBoard og Zybo med Xilinx FPGA-er .

Det gratis materialkartet , LicheeTang, av LicheePi, presentert iseptember 2018, kort som bruker en mikrokontroller basert på RISC-V-arkitekturen og bruker en FPGA, bruker en Anlogic EG4S20. Den har GPIOer for å kunne koble forskjellige typer elektroniske elementer til den.

Den Tang Nano FPGA bord , presentert ioktober 2019, fra Sipeed, bruker en GOWIN Semi GW1N FPGA fra sin LittleBee-familie .

Hummingbird E200 (eller HBird E200) prosessorkjerne-serien er en åpen kildekode-implementering av RISC-V og inkluderer FPGA- implementeringer .

I desember 2019, Presenteres OpenWiFi. Det er en gratis maskinvare og programvare WiFi-stack som kjører på FPGA, med en implementering på Xilinx.

I juni 2020, Efinix tilbyr 3 RISCV32I 32-biters arkitekturer optimalisert for Trion FPGA

I juli 2020, blir presentert open source SAVVY-V- kortet basert på PolarFire 64-bit SOC. Den PolarFire SoC Icicle benytter en FPGA SoC med 5 64-bits kjerner, inklusive en RV64IMAC og fire RV64GCs og utstyrt med to GiB av LPDDR4 RAM, først presenteres idesember 2019Han endelig sluppet den 3 th semester 2020. PolarBerry foreslås også crawdfunding variantoktober 2020.

SBC

Ulike SBC-typebrett, og kjører Linux, presenteres fra 2018, og prøver å sette en pris som ligner på den populære Raspberry Pi : SBC HiFive Unleashed (en) presenteres ifebruar 2018, basert på en SoC bestående av fire U54 RV64GC (64-biters) 1,5 GHz-kjerner og 8 GiB DDR4- type ECC RAM , på crowdfunding- basis.

Imagination Technologies og RISC-V International Open Source (RIOS) laboratoriet har gått sammen om å lage et SBC- kort kalt PicoRio , avduket iSeptember 2020på RISC-V Global Forum er plattformen generelt åpen kildekode, med unntak av visse viktige deler som I / O eller minnetilgang.

I november 2020, Kunngjør Sipeed en SBC ved hjelp av en AllWinner- enkeltkjerne SoC , sammensatt av en XuanTie C906 (RV64GCV) ved 1 GHz i 22 nm, laget av designerne av 16-kjerne RISC-V 64-biters prosessor, XT910 fra Alibaba, den har ingen 3D GPU, men en 2D GPU, og en maskinvarevideo-dekoder, H.264 og H.265, fra 64 MiB til 256 MiB loddet RAM (og noen modeller kan ha eksternt RAM), samt HDMI, Gb Ethernet, USB og USB OTG-tilkoblinger

I Januar 2021, SBC bruker en SoC BeagleV StarFive JH7100 bestående av en RISC-V-prosessor med dobbelt hjerte SiFive U74, en DSP DSP Vision Tensilica-VP6, en motor NVDLA (åpen arkitektur NVIDIA Deep Learning Accelerator) og en nevralt nettverksmotor for akselerasjon av AI. Den første versjonen har ikke en 3D-geometrisk prosessor, den andre versjonen har en GPU fra Imagination Technologies (derfor uten en åpen driver). Til slutt inkluderer SoC en VPU som er i stand til å dekode H.264 og H.265 opp til 4Kp60, eller to strømmer i 2Kp30. Kortet er utstyrt med 4 eller 8 GB RAM i LPDDR4, 4 USB 3.0-porter, en 10 GB Ethernet- port , HDMI 2.0, DSI, to ISP, en 40-pinners port og drives av USB-C. To versjoner er tilgjengelige, en med 4 GB RAM ved $ 100 og en med 8 GB for $ 150, prosessorene inngravert i 7 nm av TSMC, kjørt ved 3,5 GHz, er av typen RV64GCVBH (med spesielt en vektorenhet) og en prosessor oppnår ytelse på ARM Cortex-A76 og A77 . IMai 2021, er Fedora- distribusjonen foreslått som standarddistribusjon, med de første kartene tilgjengelige for utviklere. XFCE er standard vindusbehandling, som kan vises på HDMI-utgangen.

I Februar 2021, Pine64 , kunngjør lanseringen av en utviklings-SBC, basert på en SoC bestående av en RV64GCV-kjerne (XuanTie C906) og en andre 32-biters RISC-V BL602 ( ESP32-C ), for den trådløse nettverksdelen, driverne er under utvikling for dette en. Målet er å sette en pris lavere enn $ 15 (US), for å gjøre utviklingsplattformen tilgjengelig for så mange som mulig.

Laptop

Det kinesiske vitenskapsakademiet kunngjorde iJuni 2021, at den forbereder utgivelsen av 2000 RV64GC-baserte bærbare datamaskiner innen utgangen av 2022 og for dette arbeidet med optimalisering for RISC-V av Firefox- motorer ( spiderMonkey og dens kompakte kompilator (JIT)) og Chrome / Chromium ( WebKit ) slik at de fungerer ordentlig der.

Servere

Den Alibaba gruppe har utviklet XuanTie 910 (eller XT910), en SoC for servere , består av 16 64-bit RISC-V RV64GCV kjerner, ordnet i grupper på 4 kjerner med 32 eller 64 kb av databufferen, og så mye i bufferen. instruksjon. Gruppen hevder at ytelsen til en kjerne er av samme rekkefølge som den for en ARM Cortex-A73 .

Superdatamaskiner

Den europeiske union har lansert en superdatamaskin prosjekt basert på RISC-V arkitektur, kalt European Processor Initiative (EPI), finansiert av EU horisonten 2020-programmet, utviklet av 26 partnere (inkludert RISC-V Foundation, Centro Nacional de Supercomputación (CNS eller BSC), CEA , Infineon eller STMicroelectronics ) fra 10 land. En SoC bruker RISC-V arkitektur for akseleratorer også utviklet i Europa, har som mål å produsere en exascale superdatamaskin, samt å gi bilindustrien , basert på europeiske teknologier. Bruk av ARM-arkitektur som hovedprosessor er forutsett, men ikke sikker, i dette tilfellet ville RISC-V være begrenset til databehandlere. Prosjektet søker å gjenbruke eksisterende systemer (allerede implementert under GNU / Linux ).

Vedlegg

Merknader og referanser

- (in) " RISC-V: An Open Standard for SoCs " , EE Times (åpnet 17. august 2014 )

- (en) Lucian Armasu, “ Big Tech Players begynner å vedta RISC-V Chip Architecture ” , på Toms maskinvare ,29. november 2017

- (en) Lucian Armasu, " Nvidia-stillingsannonser peker på ambisiøse RISC-V-planer " , på Toms maskinvare ,10. oktober 2019

- (i) William G. Wong, " The Rise of RISC-V on Display at Workshop " , på ElectronicDesign ,5. desember 2017

- (i) Chris Williams, " Opp i armene! Arm dreper sitt anti-RISC-V utstrykingssted etter eget personalopprør ” , på The Register ,10. juli 2018

- (in) Joel Hruska, " ARM RISC-V dreper nettstedet etter FUD Staff Revolt " på ExtremeTech ,12. juli 2018

- (i) Nathaniel Mott, " TSMC ønsker ikke å lage sine sjetonger i USA " , på Toms maskinvare ,1 st november 2019

- (en) Nathaniel Mott, " Rapport: RISC-V planlegger å flytte fra USA til Sveits " , om Toms maskinvare ,26. november 2019

- " RISC V flytter til Sveits for å unnslippe den kinesisk-amerikanske handelskrigen " , på 01Net

- (en) Jean-Luc Aufranc, “ Hi3861-basert HiSpark WiFi IoT-utviklingskort støtter LiteOS og HarmonyOS ” , på CNX-Software ,12. oktober 2020

- (i) Gareth Halfacree, " René Rebe patcher Linux Kernel for" verdens første "Se på et Radeon 6700XT var RX RISC-V PC " på hackster.io ,21. juli 2021

- (in) " BOOM åpen kildekode RISC-V Core kjører på Amazon EC2 Instances F1 " på CNX Software ,13. desember 2018

- (en) Jean-Luc Aufranc, “ RISC-V baser og utvidelser forklart ” , på CNX-programvare ,27. august 2019

- Waterman og Asanović 2019 , s. 35.

- Jim Ledin, " The RISC-V Architecture " , på DZone ,5. juni 2020

- (i) Andrew Waterman og Krste Asanović RISC-V Instruction Set ManualVolume I: Bruker-Level ISA Document versjon 2.2 , CS Division, EECS Department, University of California, Berkeley,2017( les online ) , s. 27

- (no) kap. 5 “RV64I Base Integer Instruction Set, Version 2.1” , i RISC-V Instruksjonsmanual, Volum I: RISC-V brukernivå ISA, 20191214- desember 2019 ,desember 2019( les online )

- (in) RISC-V "V" Vector Extension ( les online )

- (in) Jon Peddie, " RV64X: A Free, Open Source GPU for RISC-V " på EE Times ,27. januar 2021

- (en) Jean-Luc Aufranc, " Think Silicon NEOX | V is the First RISC-V ISA based GPU " on CNX-Software ,4. desember 2019

- (in) " Kazan " på salsa.debian.org

- (in) " Last ned - RISC-V " på riscv.org accessdate = 17. august 2014

- Alicia Daleiden, “ Rust kommer til RISC-V, ” på Riscv.org ,28. november 2017

- Andrew Back, “ Rust kommer til RISC-V ” , på ABopen ,28. november 2017

- https://bronzebeard.readthedocs.io/en/latest/

- (in) " Minimal økosystem for RISC-V-utvikling av bart metall i python " på Python Awesome.com ,29. juni 2021

- https://github.com/theandrew168/derzforth

- " [base] Revisjon 295041 " , på svnweb.freebsd.org (åpnet 29. januar 2016 )

- " RISC-V Poster Preview - 7. RISC-V Workshop " ,28. november 2017(åpnet 17. desember 2018 )

- (in) " Gd32v " på Arduinolibraries.info

- (in) " Zephyr " på RISC-V-startveiledning (på readthedocs.io)

- (in) " Minimum Supported Version Rust (MSRV) " på Comtpe Rust innebygd på Github

- (in) oscourse-Tsinghua on Github, " RCORE "

- (in) " RISC-V er en åpen kildekodeinstruksjonsarkitektur som baner vei for de neste 50 årene med databehandling og design. » , På tessentembeddedanalytics.com

- (in) " Ghidra Software Reverse Engineering Framework " på Github

- (in) " " ghidra / Ghidra / Processors at Ghidra_9.2_build " " på siource of Ghidra code on Github ,13. november 2020(åpnet 21. november 2020 )

- (en) Jean-Luc Aufranc, " Android 10 portet til RISC-V-kort drevet av Alibaba T-Head XuanTie C910-prosessor " på CNX-programvare ,22. januar 2021

- (i) " RISC-V " på Debian .org

- https://fedoraproject.org/wiki/Architectures/RISC-V

- (no) " Ubuntu 20.04 / 21.04 64-bit RISC-V utgitt for QEMU, HiFive-kort " på CNX Software ,28. juni 2021

- https://github.com/riscv/meta-riscv

- https://wiki.freebsd.org/riscv

- https://discuss.haiku-os.org/t/my-haiku-risc-v-port-progress/10663

- https://discuss.haiku-os.org/t/my-progress-on-real-risc-v-hardware/10963/30

- https://www.youtube.com/watch?v=wHp-UIGov8c

- (in) " Komme i gang med RISC-V " på riscv.org (åpnet 17. august 2014 ) , arkiv

- (in) " riscv-tools " på riscv.org (åpnet 11. juli 2016 )

- (in) " ChangeLog / 2.12 - RISC-V " på qemu

- (in) " QEMU System Emulation User's Guide " , qemu (åpnet 31. januar 2021 )

- (in) " My Haiku RISC-V harbour progress " på Haiku-os.org

- (in) A3F, " bareDOOM " på BareDoom på Github

- (in) " JuiceVm " på juiceRv-konto på Github

- (in) " Linux 5.0 vises til å starte ESP32-prosessor " på CNX-programvare ,18. juli 2021

- (in) " riscv-rust " på Github

- Abhishek Jadhav, “ WARP-V: A RISC-V CPU Core Generator Supporting MIPS ISA ” , på CNX-programvare

- " NEORV32 RISC-V-prosessoren "

- (i) " NEORV32-prosessoren (RISC-V) " på OpenCores.org

- " The NEO430 Processor " , på Github

- (i) Gareth Halfacree, " kinesiske chip designere håper å velte Arm Cortex-A76 med Xiangshan RISC-V-design Permissively lisensiert, mål prosessorens andre iterasjon 2GHz på 14nm " , på The Register ,6. juli 2021

- (in) " PicoRV32 - En størrelse-optimalisert RISC-CPU V " på GitHub

- " Codasip muliggjør maskinvareimplementeringer av Western Digital's RISC-V SweRV Core open source " , på www.lembarque.com (Tilgang 20. mai 2021 )

- " Codasip utvider støtte for Western Digital RISC-V SweRV-kjerner til innebygde modeller , " på www.lembarque.com (Tilgang 20. mai 2021 )

- " OpenXiangShan / XiangShan " , på OpenXiangShan-konto på Github

- (zh)包 云岗, “ 首届 RISC-V 中国 峰会 2021 年 6 月 21 日 起 在 上海 举行 , 有 什么 值得 关注 的 地方? ” , på知 乎

- (en) Jean-Luc Aufranc, " XiangShan åpen kildekode 64-biters RISC-V-prosessor til å konkurrere med Arm Cortex-A76 " , på CNX-programvare ,5. juli 2021

- (in) " Chinese Academy of Sciences ga ut den innenlandske RISC-V-prosessoren" Xiangshan "qui HAR vellykket kjørt Linux, og vil bli utgitt i juli " på min.news ,2. juli 2021

- (i) Nicole Hemsoth, " Startup Takes a Risk is RISC-V Custom Silicon " , på The Next Platform ,11. juli 2016

- Alasdair Allan, “ Tar RISC-V endelig fart? » , På Hacksters.io ,19. februar 2018

- (i) " Prosessorer " på shakti.org.in

- (in) " Codasip blir med i RISC-V Foundation og kunngjør tilgjengeligheten av RISC-V Codix-kompatibel prosessor-IP " om design og gjenbruk (åpnet 20. mai 2021 )

- " Codasip lanserer 3 RISC - V-prosessorer med flere kjerner for IA Edge " , på Electronics-ECI ,8. desember 2020(åpnet 20. mai 2021 )

- " Codasip tilbyr muligheten til å øve på en reell implementering av en RISC-V-prosessor " , på www.lembarque.com (åpnet 20. mai 2021 )

- (en) Jean-Luc Aufranc, " GreenWaves GAP8 er en RISC-V IoT-prosessor med lav effekt som er optimalisert for applikasjoner for kunstig intelligens " på CNX-programvare , 27f ebruary 2018

- (en) GigaDevice Semiconductor Inc, GD32VF103 Brukerhåndbok ,oktober 2019, 533 s. ( les online )

- Gerhard Steizer, " RISC-V for alle " , på Elektronknet.de ,4. september 2019

- (en) Jean-Luc Aufranc, " GigaDevice GD32 er en raskere, programvare og Pin-to-pin kompatibel Cortex M3 STM32 MCU " på CNX-programvare ,21. desember 2015

- (i) Brian Benchoff, " New Day del: Den RISC-V Chip med innebygd Neural Networks " på Hack a Day ,8. oktober 2018

- Kadionik Patrice, " Maixduino: Do AI på en RISC-V prosessor ", hackable , n o 36 måneder = januar2021( les online )

- (i) " Kendryte K510 tri-kjerne RISC-prosessor V AI levere opp til 3 topper " på CNX Software ,9. juli 2021

- (en) Jean-Luc AUFRANC, " NodeMCU ESP32-C3 WiFi & BLE IoT-kort dukker opp for omtrent $ 4 " på CNX-Software ,12. juli 2021

- (en) Jean-Luc Aufranc, “ OpenWiFi Open-Source Linux-kompatibel WiFi Stack kjører på FPGA Hardware ” , på CNX-programvare ,16. desember 2019

- (en) Jean-Luc Aufranc, " BL602 / BL604 RISC-V WiFi & Bluetooth 5.0 LE SoC vil selge til prispoeng ESP8266 " på CNX-programvare

- (en) Jean-Luc Aufranc, " ESP32-C3 WiFi & BLE RISC-V-prosessor er pin-to-pin kompatibel med ESP8266 " på CNX-programvare ,22. november 2020

- (in) Gareth Halfacree, " Deep neurale nettverk ... I SPAAACE: Vektorforbedrede RISC-V-brikker Kan gi satellitter ombord " , på The Register ,1 st juli 2021

- Di Mascio og Al 2021 .

- (i) Gareth Halfacree, " Pine Åpner bestillinger for sin RISC-V-drevet loddebolt Pinecil Smart - med gratis Breakout Board " på Hackster.io ,25. november 2020

- (no) Jean-Luc Aufranc, " $ 3.5 RV-Debugger More JTAG debug UART & board kommer med BL702 BLE & Zigbee SoC RISC-V " på CNX-programvare ,21. juni 2021

- (in) " LicheeTang Anlogic EG4S20 FPGA Board Targets RISC-V Development " på CNX Software ,4. september 2018

- “ $ 5 Tang Nano FPGA Board har GOWIN GW1N“ LittleBee ”FPGA ” , på CNX Software ,15. oktober 2019

- (en + zh) “ Hummingbird E200 Opensource Processor Core ” , på GitHub

- (en) Jean-Luc Aufranc, " Efinix lanserer tre RISC-V programvaredefinerte SoC-er optimalisert for FPGAs Trion " på Cnt-programvare ,6. juni 2020

- (en) Jean-Luc Aufranc, " PolarBerry er en kompakt RISC-V FPGA-modul og SBC (Crowdfunding " på CNX Software , Linux-kompatibel .5. juli 2020

- (en) Jean-Luc Aufranc, " PUpcoming SAVVY-V Open Source RISC-V Cluster Board støtter 10GbE via Microsemi PolarFire 64-bit RISC-V SoC " på CNX Software ,20. juli 2020

- (en) Jean-Luc Aufranc, " PolarBerry er en kompakt RISC-V FPGA-modul og SBC (Crowdfunding " på CNX Software , Linux-kompatibel .30. oktober 2020

- (en) Jean-Luc Aufranc, " SiFive Introduces HiFive Unleashed RISC-V Linux Development Board (Crowdfunding) " på CNX Software ,4. februar 2018

- (en) Jean-Luc Aufranc, " PicoRio Linux RISC-V SBC er et åpen kildekodealternativ til Raspberry Pi-kort " på CNX-programvare ,4. september 2020

- Jean-Luc Aufranc, " XuanTie C906-basert Allwinner RISC-V-prosessor for å drive $ 12+ Linux SBC-er " , på CNX-programvare ,9. november 2020

- Jean-Luc Aufranc, “ $ 119 + BeagleV kraftig, åpen hardware RISC-V Linux SBC målretter AI-applikasjoner ” , på CNX-programvare ,13. januar 2021

- (in) Chloe Ma, " RISC-V Star Rising from the East - Introducing StarFive " på riscv.org ,1 st mars 2021

- (zh) " 重磅 " , på Starfive-konto på Weixin ,10. desember 2020

- (in) Starfive Tech, " BeagleV Starlight RISC-V Fedora picture " på Gihtub

- (in) PINE64, " Februar Update: Show and Tell " på Pine64.org

- (i) Gareth Halfacree, " Kinas Iscas å bygge 2000 RISC-V bærbare datamaskiner ved utgangen av 2022 som nasjon forsøker å kutte avhengigheten er Arm, Intel-prosessorene " , på The Register ,8. juni 2021.

- (en) Jean-Luc Aufranc, " Flere detaljer om Alibaba XT910 64-bit RISC-V Core " på CNX Software ,25. august 2020

- (in) " Hvordan European Initiative Processor Leveraging is RISC-V for the Future of Supercomputing " på Inside HPC ,22. august 2019

Bibliografi online

-

(en) “ Spesifikasjoner ” , på riscv.org

- (en) Andrew Waterman og Krste Asanović, The RISC-V Instruction Set Manual - Volume I: Unprivileged ISA , CS Division, EECS Department, University of California, Berkeley,desember 2019( les online )

- (en) Andrew Waterman og Krste Asanović, The RISC-V Instruction Set Manual - Volume II: Privileged Architecture , CS Division, EECS Department, University of California, Berkeley,juni 2019( les online )

- (en) Krste Asanović (en) og David Patterson , instruksjonssett bør være gratis: saken for RISC-V , elektroteknikk og informatikk ved University of California i Berkeley,august 2014( online presentasjon , les online )

- (Utfaset) RISC-V instruksjonssett HotChips 25 (2013)

- RISC-V Software Ecosystem HPCA 2015, Tutorial

- Yunsup Lee, RISC-V "Rocket Chip" SoC Generator i Chisel , UC Berkeley, HPCA,2015( les online )

- (en) d0iasme, Skrive en RISC-V-emulator i rust ( les online )( kilde )

- (en) Hiroaki Kaneko et Akinori Kanasugi, en integrert maskinkodemonitor for en RISC-V-prosessor på en FPGA , SpringerLink,2020( ISSN 1614-7456 , OCLC 1196515116 )

- (en) Johannes Geier, Fast RTL-basert feilinjeksjonsrammeverk for RISC-V-kjerner , München, Masterarbeit Technische Universität,2020( OCLC 1193312286 )

- (no) SHAKTI Development Team, RISC-V Assembly Language: Programmer Manual Part I , Madras, SHAKTI Development Team,2020( les online )

- (en) Stefano Di Mascio, Alessandra Menicucci, Eberhard Gill, Gianluca Furano og Claudio Monteleone, " On-Board Decision Making in Space with Deep Neural Networks and RISC-V Vector Processors " , Journal of Aerospace Information Systems ,Juni 2021( DOI 10.2514 / 1.I010916 , online presentasjon , les online )

Bibliografi på papir

Virker- (no) Andrew Shell Waterman, Design of the RISC-V Instruction Set Architecture , Berkeley, CA,2016( OCLC 957714390 ) (avhandling for en doktorgrad i Computer Science University of California, Berkeley 2016)

- (en) John L. Hennessy og David A. Patterson, Computer Organization and Design RISC-V Edition , Morgan Kaufmann,april 2017, 696 s. ( ISBN 978-0-12-812275-4 , e-ISSN 978-0-12-812276-1 [sjekk: Ugyldig ISSN ] )

- (zh-Hans)胡振波,手把手教 你 设计 CPU : RISC-V 处理器 篇, 北京, 人民 邮电 出版社,Mai 2018, 480 s. ( ISBN 978-7-115-48052-1 , online presentasjon )

- (ja)デ イ ビ ッ ド パ タ ー ソ ソ (David A Patterson) og ア ン ド リ ュ ー ウ ウ ォ ー タ ー マ Andrew (Andrew Waterman) ( overs. 成 田光彰 (Narita)), RISC -V 原 典 (リ ス ク フ ァ イ ブ 原典): オ ー プ ン · ア ー キ テ ク チ ャ のス ス メ, 日 経 BP2018, 224 s. ( ISBN 978-4-822292-812 )

- Gaétan Kuetche Saadeu, Design of a RISC-V multi-core microcontroller Introduction to the design of a microcontroller using Arduino Shields , Saarbrücken, European University Publishing,2019( ISBN 9786139502493 )

- (en) John L Hennessy og David A Patterson, Computer architecture: a quantitative approach , Cambridge, Massachussetts, Elsevier, coll. "Morgan Kaufmann-serien i dataarkitektur og design",2019( ISBN 9780128119068 )

- (zh-Hans)胡振波, RISC-V 架构 与 嵌入式 开发 快速 入门, 北京, 人民 邮电 出版社,2019, 354 s. ( ISBN 9787115494139 )

- (en) Anthony J Dos Reis, RISC-V forsamlingsspråk , USA,2019, 149 s. ( ISBN 9781088462003 )

- (en) Jim Ledin, Modern Computer Architecture and Organization: Learn X86, ARM, and RISC-V Architectures and the Design of Smartphones, PCs, and Cloud Servers , Birmingham, Packt Publishing,2020( ISBN 978-1-838987-107 )

- Shruthi K Muchandi, muliggjør Accelerator-SoC Co-design ved bruk av RISC-V Chipyard , Charlotte, University of North Carolina,2020( ISBN 9781392495506 )

- (en) Jing Chen, maskinvareakselerasjon for grunnleggende funksjoner og RISC-V-prosessor , Montreal, McGill University Libraries,2020( OCLC 1199006597 )

- (en) Vladimir Herdt, Daniel Große og Rolf Drechsler, Enhanced Virtual Prototyping: Featuring RISC-V Case Studies , Cham, Springer,2021( ISBN 978-3-030-54827-8 , DOI 10.1007 / 978-3-030-54828-5 )

- Kadionik Patrice, " Maixduino: do AI på en RISC-prosessor V ", hackable , n o 36,Januar 2021( les online )

Eksterne linker

- http://riscv.org/ - Offisielt nettsted

- http://www.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-146.pdf - RISC-V instruksjonssett og sammenligninger med andre lignende arkitekturer.

- https://riscv.org/software-tools/riscv-angel/ - ANGEL, RISC-V instruksjonssett HTTP-simulator

- (no) “ Analysering av RISC-V-instruksjonsarkitekturen ” , på Adapteva - sammenligning mellom RISC-V-arkitekturen (32-biters versjon) og Adapteva- arkitekturen.

- (en) " RISC-V " , på wiki.debian.org Debian Port på RISC-V

- (no) " RISC-V Cores and SoC Overview " , på Awesome Open Source - Liste over implementeringer